Memory

#### اقتصاديات الذاكرة:

## جدول مبيعات USA من الدارات المتكاملة عام ١٩٩٠:

| category                    | #(in billion) |

|-----------------------------|---------------|

| DRAM                        | 2.84 (60%)    |

| SRAM                        | 0.75 (16%)    |

| ROM                         | 1.19 (24%)    |

| Custom ICs (PAL,)           | 2,93 (25%)    |

| μPs (486,)                  | 2.56 (22%)    |

| Digital ffamilies (TTL,)    | 1.07 (9%)     |

| Special Purpose Pro. (DSP,) | 0.51 (4%)     |

4.78 40% من لاجمال*ي*

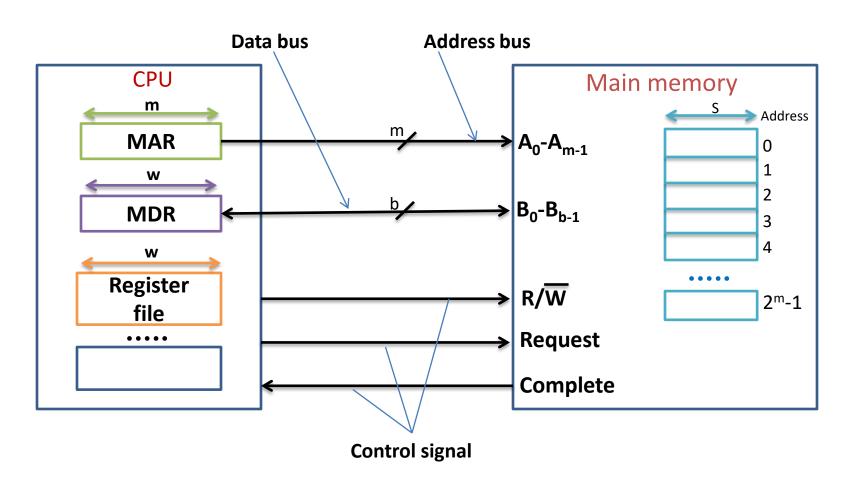

# المخطط الصندوقي للذاكرة الرئيسية main memory

معالج له m خط عنونة، يستطيع عنونة ذاكرة بسعة 2<sup>m</sup>كل منها بطول S خانة.

### تتم عمليتي القراءة والكتابة كالتالي:

- القراءة: يتم وضع عنوان موقع الذاكرة في MAR ينشأ طلب من الذاكرة وتفعل R لتحديد العملية أنها قراءة ويُرسل العنوان على مسرى العناوين بعدها ترفع محتويات الموقع على مسرى البيانات وتخزن مؤقتاً في MDR بعدها ينشأ أمر complete.

- الكتابة: يتم وضع عنوان موقع الذاكرة المراد الكتابة فيه في MAR ثم ينشأ طلب من الذاكرة و تفعل w لتحديد العملية أنها كتابة وتكون البيانات المراد كتابتها في MDR، يُرسل العنوان وتدخل البيانات الى موقع الذاكرة وتفعل إشارة complete.

- عملية القراءة nondestructive وعملية الكتابة

پُحسب حجم الذاكرة (الخانة) كالتالي:

سعة الذاكرة (الخانة)= 2<sup>m</sup> × S

• مثال: معالج Motorola) power pc 601

فيه عدد خطوط العنونة m=32 (حجم MAR) و S=8 bit (حجم كلمة الذاكرة) فما هو حجم الذاكرة الممكن عنونتها؟

سعة الذاكرة التي يستطيع المعالج عنونتها = 232 × 8 bit

- ﴿ زَمِنَ الْوصولِ access time t<sub>a</sub>: هو الفترة الزمنية من بدء عملية القراءة حتى لحظة ارسال اشارة اتمام complete

- ﴿ زمن دورة القراءة والكتابة cycle time tc: هو الزمن الأصغري من بدء عملية قراءة او كتابة حتى بدء عملية اخرى مماثلة

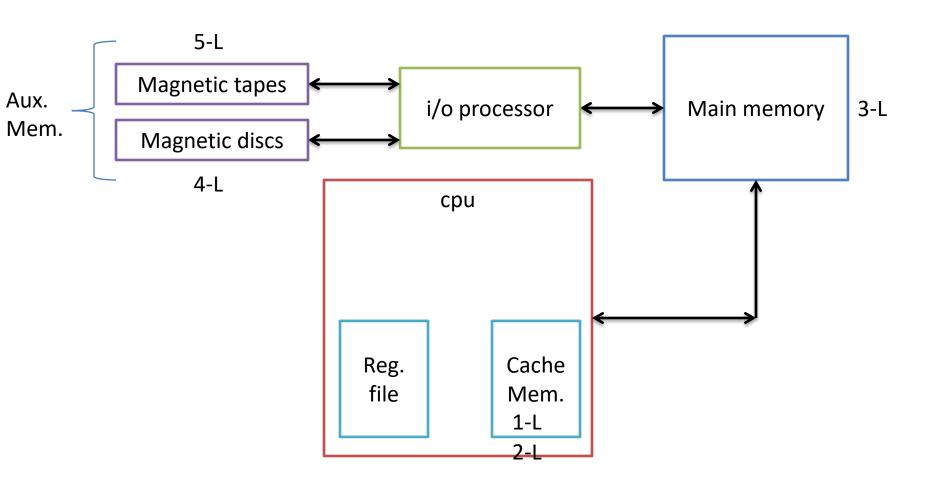

# هرمية الذاكرة: Memory hierarchy

- تستخدم الحواسيب انواع مختلفة من الذواكر لتشغيل برامجها وتخزين معطياتها.

- تدعى الذاكرة الموصولة مع المعالج بالذاكرة الزمنية (تحتوي على البرامج ومعطياتها).

- تدعى الذواكر التي تحتفظ بنسخ من البرامج والمعطيات بالذواكر المساعدة (الاقراص الممغنطة والليزرية و ...).

- يعرف التأخير latency: على أنه الزمن المطلوب لادخال أول تتابع من الكلمات من وحدات الذاكرة المختلفة الى المعالج.

#### Memory hierarchy

| Latency | Cpu regester | cache  | Main mem. | Hard disk | Tape mem.      |

|---------|--------------|--------|-----------|-----------|----------------|

| (acces  | 1-10(ns)     | 20(ns) | 50(ns)    | 10(ms)    | 10(ms)-10(sec) |

| time)   |              |        |           |           |                |

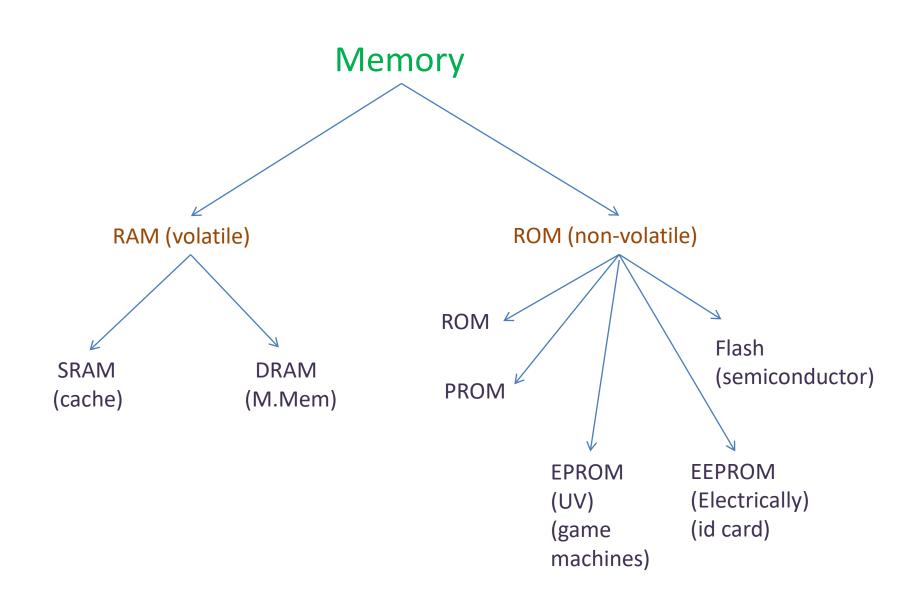

## تصنيف الذواكر المصنوعة من مواد نصف ناقلة:

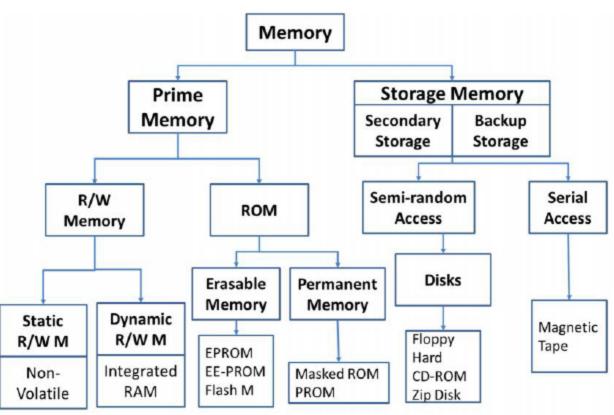

# تصنيف الذواكر في الحاسب

**Figure: Classification of Memory**

## البنية الداخلية للذاكرة RAM: RAM البنية الداخلية للذاكرة

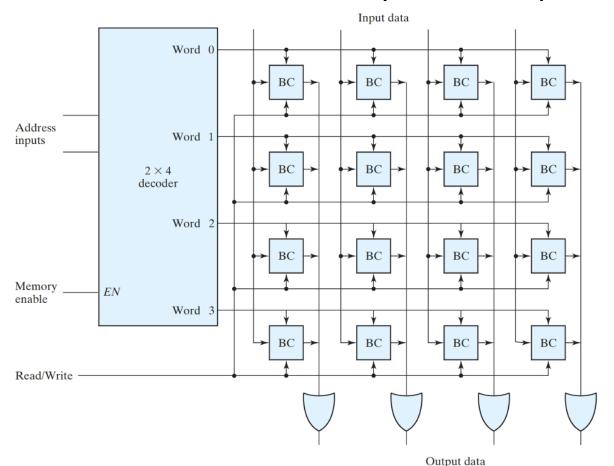

المخطط التالي يوضح بنية ذاكرة RAM بـ 16 خانة (4 words ×4 bits)

**Block Diagram of 4×4 RAM**

Control Inputs to Memory Chip

| Memory Enable | Read/Write | <b>Memory Operation</b> |

|---------------|------------|-------------------------|

| 0             | х          | None                    |

| 1             | 0          | Write to selected word  |

| 1             | 1          | Read from selected word |

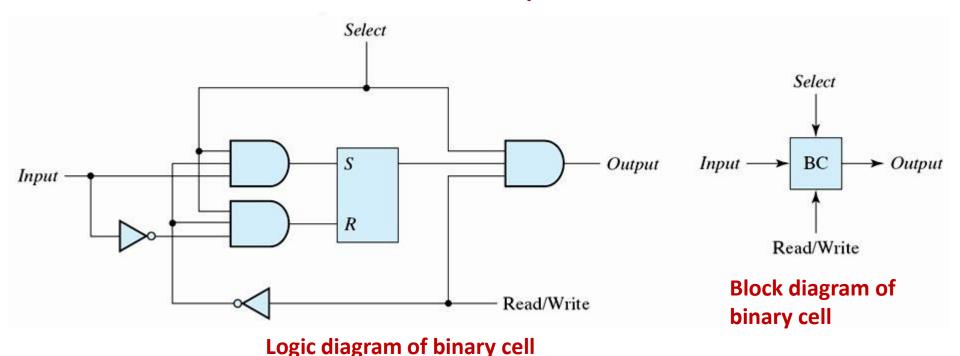

#### Memory cell

المدخل select: يسمح بالقراءة أو الكتابة من الخلية.

الخط read/write هو خط تحكم:

بوضع 1 عليه تتم عملية القراءة ويحدث ممر ما بين خرج القلاب وطرف خرج الخلية output. بوضع 0 عليه تتم عملية الكتابة ويحدث ممر ما بين الدخل input الى القلاب.

## توسیع ذواکر RAM مصفوفة من شرائح Array of RAM Chips RAM

- ح توجد ذواكر RAM بأحجام مختلفة، إذا كان حجم الذواكر المطلوب لتطبيق ما لا يكفي يمكننا دمج عدد من هذه الذواكر.

- ح تعتمد سعة ذاكرة ما على عدد الكلمات وعدد خانات كل كلمة.

- ﴿ زيادة عدد الكلمات للذاكرة يقتضي زيادة طول العنوان حيث تضاعف كل خانة مضافة للعنوان عدد الكلمات في الذاكرة.

- ريادة عدد خانات كل كلمة يقتضي أن نزيد طول خطوط دخل وخرج البيانات مع بقاء طول العنوان نفسه.

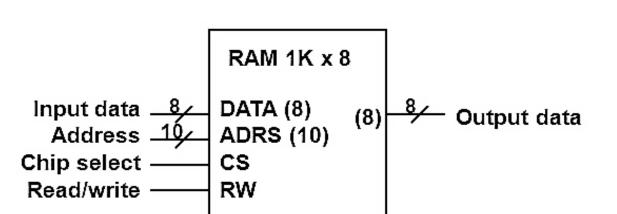

#### مثال

لشريحة RAM النموذجية (1024words×8bits)

مسری عنونة بـ 10خطوط ومسری بیانات بـ 8 خطوط

المطلوب: باستخدام هذه الشريحة حقق

أ- ذاكرة بـ 4 kB

ب- ذاكرة بعرض كلمة قدره 16 bit

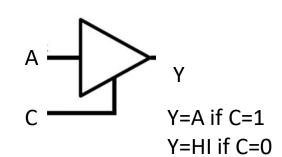

0, 1, high impedance Z (open)

cs مدخل اختيار الشريحة

CS=0 لا يتم اختيار الشريحة وتكون حالة مخارجها في حالة الممانعة العالية

CS=1 R/W=1 تتم القراءة من الذاكرة حسب العنوان المحدد من مسرى العناوين

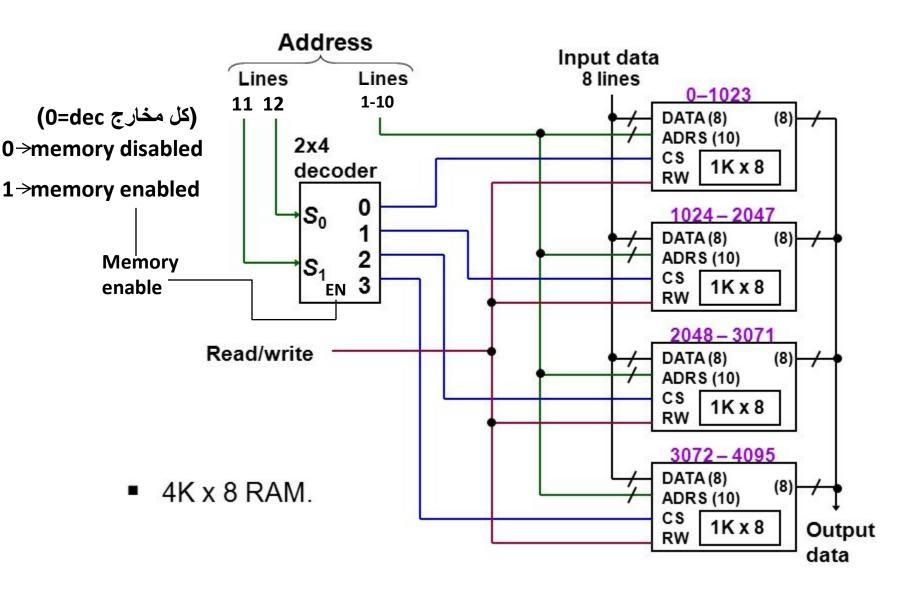

#### بناء ذاكرة 8×4K من الذاكرة السابقة (زيادة حجم الذاكرة)

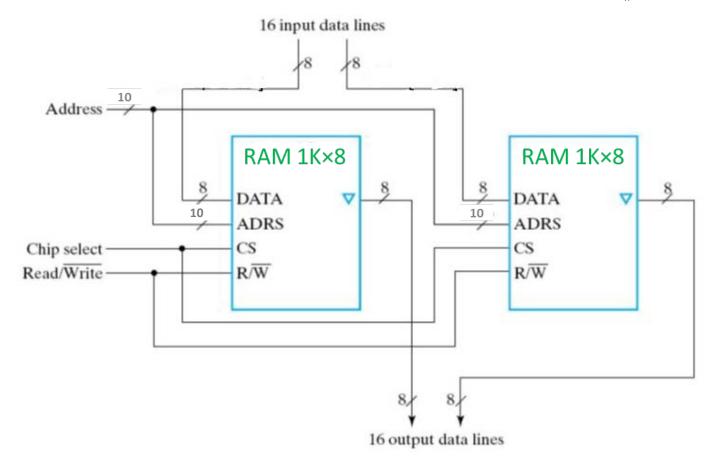

#### زيادة عدد خانات الكلمة الواحدة: ذاكرة (1k×16bit)

تطلب عملية زيادة عدد خانات الكلمة الواحدة زيادة عدد خطوط المعطيات لكل من الدخل والخرج

المخطط الصندوقي لذاكرة 16bit المخطط

نلاحظ ان كلا الشريحتين يستقبل العنوان ذو الـ 10 bit (الكافي لعنونة 1K word) يمكن دمج الطريقتين السابقتين للحصول على ذواكر بحجوم وكلمات اكبر.

### كشف الخطأ وتصحيحه Error detection and correction

- إن مستوى تعقيد مصفوفة الذاكرة يمكن أن يسبب اخطاء في بعض الاحيان اثناء تخزين أو استرجاع المعلومات.

- يمكن أن تتحسن وثوقية الذاكرة باستخدام شيفرات تصحيح وكشف الخطأ

- الطريقة العامة المشهورة لكشف الخطأ هي خانة التماثل (parity bit).

- و تولد خانة التماثل وتخزن مع خانات المعطيات في الذاكرة.

- خانة التماثل هي خانة إضافية تدخل مع الكلمة الثنائية لتجعل عدد الواحدات فيها اما فردياً أو زوجياً لذلك نميز بين:

- ✓ تماثل فردي: عدد الواحدات في الكلمة بما فيها خانة التماثل فردي (odd parity)

- √ تماثل زوجي: عدد الواحدات في الكلمة بما فيها خانة التماثل زوجي (even parity)

- يتم ارسال الكلمة مع خانة التماثل من طرف المرسل ويقوم المستقبل بفحص هده الخانة فلو انها ذات تماثل يكون قد حدث خطأ ما.

- لذا نحن نحتاج:

- ✓ دارة لتوليد خانة التماثل من طرف المرسل (دارة مولد التماثل parity generator)

✓ ودارة لكشف التماثل في طرف المستقبل (دارة فاحص التماثل parity checker)